## FUTURE HPC TECHNOLOGIES

The current technologies used for HPC systems will not be able to sustain the performance increase requested by the HPC/HPDA/Al<sup>1</sup> application communities. Since the end of the Dennard scaling and with the approaching end of the Moore's law, the standard CMOS<sup>2</sup> technology has to be complemented by other approaches if we want to continue to deliver more performance.

The three main HPC ecosystems beside Europe, namely US, China and Japan have undertaken significant research initiatives to work on these new approaches. The investigations include topics such as new materials that are more efficient than CMOS, new architecture, photonics, analogue system or quantum technologies. The level of investment is high in these three countries but we do not believe that they have already a competitive edge over Europe.

This white paper presents first why is it mandatory to look for new HPC technologies. After a short presentation of the international landscape, we review the research options that could sustain the development of HPC. This analysis is the result of a work organized by EXDCI-2 to connect the HPC communities with the European electronics and photonics experts.

The last section presents some recommendations for Europe to strengthen its position in technologies relevant for future HPC system. These recommendations could be implemented through EuroHPC actions and/or initiatives of the future Horizon Europe programme.

<sup>&</sup>lt;sup>1</sup> High Performance Computing/ High Performance Data Analytics/ Artificial Intelligence

<sup>&</sup>lt;sup>2</sup> Complementary Metal Oxide Semi-conductor

## Table of contents

| Why do we need new technologies for future HPC systems?        | 3  |

|----------------------------------------------------------------|----|

| International landscape                                        | 10 |

| USA                                                            | 10 |

| China                                                          | 14 |

| Japan                                                          | 15 |

| Potential options for the future HPC technologies              | 19 |

| Introduction                                                   | 19 |

| Enhancements of current CMOS technologies                      | 20 |

| New architectures                                              | 22 |

| Hybrid of CMOS and other technologies: NVMs, silicon photonics | 25 |

| New solutions more efficient than CMOS                         | 26 |

| Analogue computing                                             | 28 |

| New computing paradigm: quantum computing                      | 28 |

| Transversal questions                                          | 29 |

| Summary                                                        | 31 |

| Conclusion and recommendations                                 | 32 |

## List of figures

| Figure 1: "Classical scaling" and "Curent scaling"                                                      | 3   |

|---------------------------------------------------------------------------------------------------------|-----|

| Figure 2: Evolution of processors over time                                                             | 4   |

| Figure 3: energy consumption of ICT (from Nature, September 12, 2018)                                   | 5   |

| Figure 4: cost of moving data                                                                           | 6   |

| Figure 5: Evolution of computing systems over time, driven by more and more efficiency (picture from De | nis |

| Dutoit, CEA)                                                                                            | 7   |

| Figure 6: optical interconnect is efficient down to board, and perhaps to chip, where a serdes (electri | cal |

| interconnect) is replaced by a Photonic Interconnect Circuit (PIC)                                      | 8   |

| Figure 7: or efficient even at the chiplet level, with a photonic interposer                            | 8   |

| Figure 8: the Fujitsu A64FX chip, core of the Fugaku computer                                           | 16  |

| Figure 9: Nominal vs. actual node dimensions (Source: CEA Leti)                                         | 20  |

| Figure 10: NeuRAM3 approach                                                                             | 24  |

| Figure 11: Potential future architecture of an HPC node with several accelerators                       | 30  |

# Why do we need new technologies for future HPC systems?

#### The end of Dennard scaling and excessive cost of Moore's law:

Moore's law<sup>3</sup> was for a long time accompanied by Dennard's law, i.e. doubling the operating frequency of the processors with each generation was related to voltage reduction resulting in a constant energy density. The IC architects therefore experienced a few tens of years of "happy scaling" where performance was automatically improved with an increase of the frequency and number of transistors without impacting power consumption (see Figure 1). In the 2000s, the frequency stabilized and multi-core architectures were developed in accordance with Moore's law: as you can still increase the number of transistors per mm<sup>2</sup>, but they cannot go faster, the logical idea is to duplicate the computing resources. However, the supply voltage now remains almost constant across generations of technology, which consequently increases the energy density in active mode. In addition, the thinness of the transistors drastically increases the leakage current which become predominant. Today, we have reached the dissipation limits of silicon. Therefore, the main challenge is now to reduce power consumption in integrated circuits, which will also stabilize the TCO (total Cost of Ownership) of "computing" and HPC centres by reducing the electricity bill.

| Parameter<br>(scale factor = a) | Classic<br>Scaling | Current<br>Scaling |

|---------------------------------|--------------------|--------------------|

| Dimensions                      | I/a                | I/a                |

| Voltage                         | I/a                | I.                 |

| Current                         | I/a                | I/a                |

| Capacitance                     | I/a                | >1/a               |

| Power/Circuit                   | I/a <sup>2</sup>   | I/a                |

| Power Density                   | I.                 | a                  |

| Delay/Circuit                   | I/a                | ~1                 |

FIGURE 1: "CLASSICAL SCALING" AND "CURENT SCALING"<sup>4</sup>

<sup>&</sup>lt;sup>3</sup> These are called « laws » but they are not physics law, only observation and forecasts.

<sup>&</sup>lt;sup>4</sup> "classical scaling" shows the parameters when Dennard's scaling was still active, when the geometrical size of the technology (the technology "node"4) was reduced by factor "a". "Current scaling" shows the evolution of the parameters on small technology nodes, where Dennard's scaling is not anymore valid.

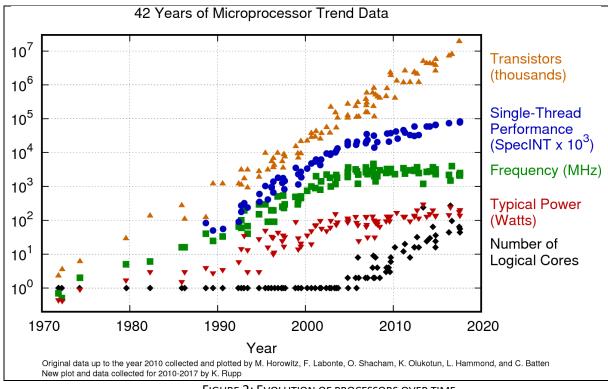

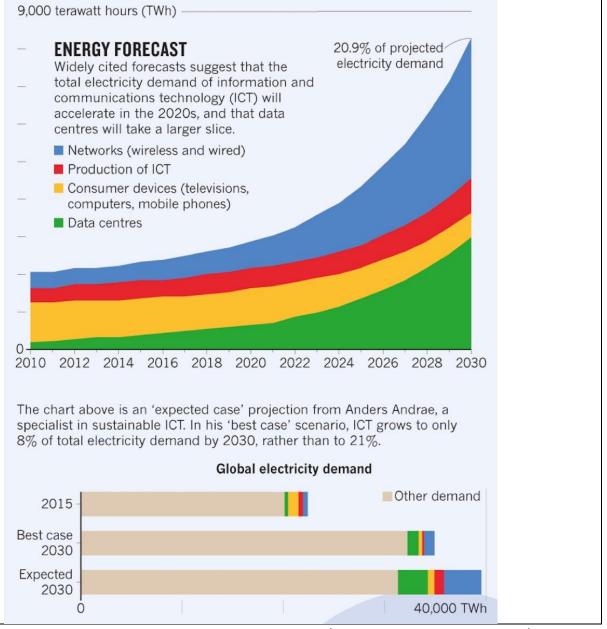

Figure 2 shows the consequences on the performance of microprocessors: from about 2005 the frequency of processors stops increasing, and as the number of transistors can still increase (Moore's law) the number of cores per processor increased, while the power dissipation reaches the limit of what can be dissipated at affordable cost per chip. To further increase the global system performance, the number of processors drastically increased in HPC and datacenters, with a correlated increase of power consumption. It is believed that 30 to 50 MW is the practical limit for the consumption of a HPC or datacenter, and it is the main practical limitation for exascale machines: reaching an energy efficiency that allow having exascale capabilities in this power and dissipation budget. It is also why there is a concern about the power consumption of ICT (see Figure 3).

FIGURE 2: EVOLUTION OF PROCESSORS OVER TIME

FIGURE 3: ENERGY CONSUMPTION OF ICT (FROM NATURE, SEPTEMBER 12, 2018)

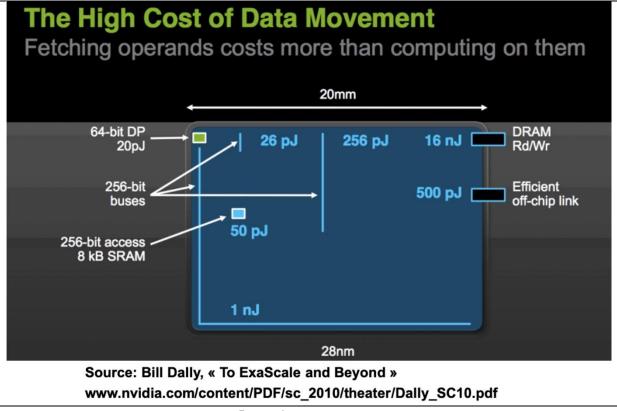

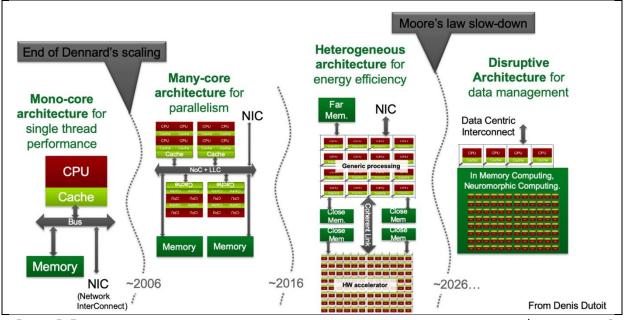

If we analyse the source of energy dissipation in more details, we see that transfer of data are the main source of loss and heat generation: Figure 4 shows that getting data from external DRAM takes 800 times more energy than making operations on those 64 bit data extracted from the DRAM. This is the drive of the approach of chiplets and interposers, where different "chips" are connected on a silicon interposer with a much smaller footprint than with a PCB (Printed Circuit Board). It also drives emerging architectures where computing and storage are more intertwined, like in "near memory computing", "in memory computing" or "processing in memory" architectures. Figure 5 shows this potential evolution over time, where the end of Dennard's scaling drove a rise in many-core architectures, the quest for better efficiency introduced heterogeneous

architectures with a plurality of co-processors or accelerators, then a possible rise of processing in memorybased systems.

However, there is another way to decrease the energy consumption of moving data: using photons instead of electrons.

FIGURE 4: COST OF MOVING DATA

FIGURE 5: EVOLUTION OF COMPUTING SYSTEMS OVER TIME, DRIVEN BY MORE AND MORE EFFICIENCY (PICTURE FROM DENIS DUTOIT, CEA).

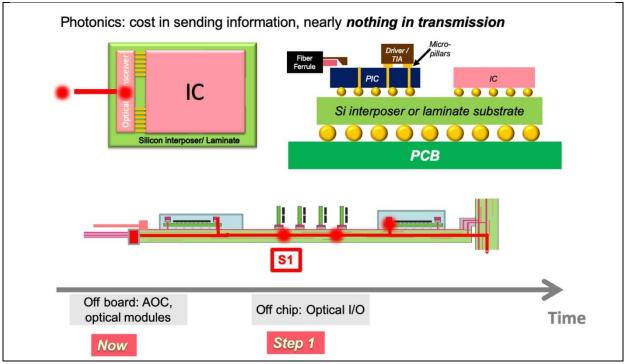

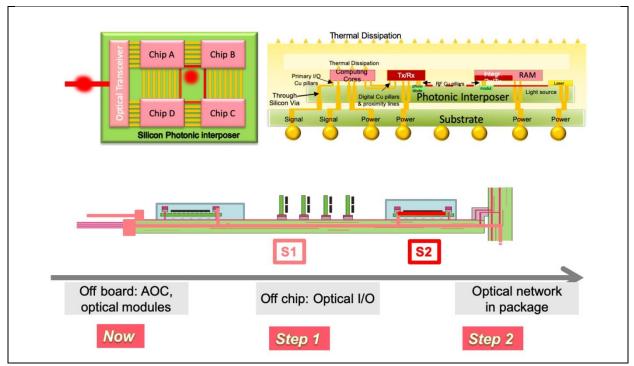

Electrons require little energy to create a signal and receive it, but Ohm's law means that the transmission of electrons results in the dissipation of a lot of energy. On the contrary, photons are relatively expensive to create (lasers) or to receive (sensors), but once created, they can travel on long distance with minimal attenuation. A factor, expressed in Mbit per second per km and per watt, once reached, means that optics are more efficient than electronics at transmitting information. As the throughput of current systems is always increasing, the distance where optics are efficient decreases, perhaps down to interconnecting chiplets on an interposer, as shown in Figure 6 and Figure 7.

Without even considering computing with photons, we can see that there is a strong rationale to look for synergies between photonics and electronics for very high performance systems that will process a very large amount of data.

FIGURE 6: OPTICAL INTERCONNECT IS EFFICIENT DOWN TO BOARD, AND PERHAPS TO CHIP, WHERE A SERDES (ELECTRICAL INTERCONNECT) IS REPLACED BY A PHOTONIC INTERCONNECT CIRCUIT (PIC).

FIGURE 7: OR EFFICIENT EVEN AT THE CHIPLET LEVEL, WITH A PHOTONIC INTERPOSER.

In summary, in the post-exascale time frame, HPC system performance will not increase any further using the current technologies. There is a need for new solutions that can come from new heterogeneous architectures and new research paths being explored mainly by the photonics and electronics communities.

## International landscape

Before discussing the European situation, it is interesting to look at what is going on in the main international HPC ecosystems. For this analysis, we have focused on the US, China and Japan which are the countries with the most advanced programmes for post exascale HPC technologies.

#### USA

The United States, as usual in Information Technology, has been the first ecosystem to acknowledge that a disruption has to happen to sustain the growth in performance of HPC systems. Several reports have been issued for high level advisory committees. One of them "Future High Performance Computing Capabilities" was issued as a "Summary Report of the Advanced Scientific Computing Advisory Committee (ASCAC)<sup>5</sup>" back in 2017. These reports were the starting point of actions to launch ambitious research programmes. DARPA (Defense Advanced Research Projects Agency) is very active in this field and has launched several programmes relevant for HPC that are having a broad impact way beyond the defense domain:

- ERI Electronics Resurgence Initiative<sup>6</sup>

- ACCESS Accelerated Computation for Efficient Scientific Simulation<sup>7</sup>

- PIPES Photonics in the Package for Extreme Scalability<sup>8</sup>

A short description of these programmes can be found below.

#### ERI

Announced in 2017, ERI is a five-year, upwards of \$1.5 billion investment to jumpstart innovation in the electronics industry. To address the impending engineering and economic challenges confronting those striving to push microelectronics technology forward, DARPA is nurturing research in circuit design tools, advanced new materials, and systems architectures through a mix of new and emerging programmes. The first phase of ERI is organized around 6 programmes:

<sup>5</sup>

<sup>&</sup>lt;sup>5</sup> https://science.osti.gov/-/media/ascr/ascac/pdf/meetings/201712/ASCAC-Future-HPC-report.pdf?la=en&hash=2FEB999A02D5D4C30EAC01A0C090AAFCC49996E9

<sup>&</sup>lt;sup>6</sup> https://www.darpa.mil/work-with-us/electronics-resurgence-initiative

<sup>&</sup>lt;sup>7</sup> https://www.darpa.mil/program/accelerated-computation-for-efficient-scientific-simulation

<sup>&</sup>lt;sup>8</sup> https://www.darpa.mil/program/photonics-in-the-package-for-extreme-scalability

- Materials & Integration

- Monolithic Integration of an SoC in Three Dimensions (3DSoC)

- Framework for Novel Compute (FRANC)

- Architecture:

- Software Defined Hardware (SDH)

- Domain-Specific System on Chip (DSSoC)

- Design

- Intelligent Design of Electronic Assets (IDEA)

- Posh Open Source Hardware (POSH)

The Three Dimensional Monolithic System-on-a-Chip (3DSoC) programme seeks to develop the monolithic 3D technology required to build logic, memory, and input/output (I/O) on a single die using a legacy lithography node while improving performance by more than 50X when compared with leading edge technology nodes. To achieve its goals, 3DSoC seeks to develop fabrication technology as well as the design flows required to take advantage of the technology's capabilities.

The Foundations Required for Novel Compute (FRANC) programme aims to develop innovative approaches to advance compute technologies beyond the Von Neumann topology. Leveraging recent advances in materials, devices, and integration technology, the programme seeks to develop novel memory-centric compute topologies that break the traditional separation of processors and memory components to realize dramatic advances in compute efficiency and throughput of the workload, especially for applications constrained by size, weight, and power (SWaP). Innovative compute architectures and new, fast non-volatile storage and memory-centric computing devices will be explored under FRANC to enable low latency compute near or inside the data storage elements. Such approaches are particularly suited for applications relevant to artificial intelligence (AI) where in-memory computation provides unique advantages over traditional Von Neumann computation.

The goal of the Software Define Hardware (SDH) programme is to build runtime-reconfigurable hardware and software that enables near ASIC<sup>9</sup> performance without sacrificing programmability for data-intensive algorithms. Under the programme, data-intensive algorithms are defined as machine learning and data science algorithms that process large volumes of data and are characterized by their usage of intense linear algebra, graph search operations, and their associated data-transformation operators. The SDH programme aims to create hardware/software systems that allow data-intensive algorithms to run at near ASIC efficiency without the cost, development time, or single application limitations associated with ASICs.

Domain-Specific System on Chip (DSSoC) intends to demonstrate that the trade-off between flexibility and efficiency is not fundamental. The programme plans to develop a method for determining the right amount and type of specialization while making a system as programmable and flexible as possible. DSSoC wants to de-couple the programmer from the underlying hardware with enough abstraction but still be able to utilize the hardware optimally through intelligent scheduling. DSSoC specifically targets embedded systems where the domain of applications sits at the edge and near the sensor. Workloads consist of small chunks of data but

<sup>&</sup>lt;sup>9</sup> Application Specific Integrated Circuit

often with a large number of algorithms required in the processing, meaning that high compute power and low latency at low power are required.

The Intelligent Design of Electronic Assets (IDEA) programme seeks to develop a general purpose hardware compiler for no-human-in-the-loop translation of source code or schematic to physical layout (GDSII) for SoCs, System-In-Packages (SIPs), and Printed Circuit Boards (PCBs) in less than 24 hours. The programme aims to leverage advances in applied machine learning, optimization algorithms, and expert systems to create a compiler that could allow users with no prior design expertise to complete physical design at the most advanced technology nodes.

The Posh Open Source Hardware (POSH) programme seeks to enable mathematically provable secure electronics and create an open source hardware IP ecosystem, along with accompanying validation tools. Under the programme, researchers will work to develop methodologies, standards, and simulation as well as emulation technologies for the verification and mathematical inspection of analogue and digital IP to provide proof of functionality and security. The program also aims to develop and release a number of silicon-proven analogue and digital IP blocks on an open source platform to serve as a foundation for rapid design of complex secure SoCs at leading edge technology nodes.

The initial programmes are expected to be followed by additional initiatives such as PIPES (see section 2.1.3).

#### ACCESS

In comparison to ERI, ACCESS is a much smaller programme but it is interesting because it illustrates well the objective of finding disruptive computing solutions. The budget of ACCESS is small (in the range of \$1M for each project) and it has the rather focused objective of developing technologies for the acceleration of scientific simulations of physical systems characterized by coupled partial differential equations (PDEs).

The Accelerated Computation for Efficient Scientific Simulation (ACCESS) programme seeks innovative ideas for computational architectures that will achieve the equivalent of petaflops performance in a benchtop form-factor and be capable of what traditional architectures would define as "strong" scaling for predictive scientific simulations of interest.

The design and development of the prototypes are envisioned to leverage advances in optics, MEMS, additive manufacturing, and other emerging technologies to develop new non-traditional analogue and digital computational means and to overcome some of the current known limitations of these means, such as precision and stability. Of particular interest are hybrid analogue/digital architectures that replace numerical methods and memory-intensive computational parallelization with nonlinear and/or intrinsically parallel physical processes to perform computations.

Unfortunately, we have not been able to find the list of the projects funded by this programme.

#### PIPES

After the ERI first phase and the launch of 6 research areas (see section above), it appears that other domains have to be investigated to complement this first effort. Photonics was one of these and the ERI phase II includes a new programme PIPES for this field.

The Photonics in the Package for Extreme Scalability (PIPES) programme, seeks to enable future system scalability by developing high-bandwidth optical signalling technologies for digital microelectronics. Working across three technical areas, PIPES aims to develop and embed integrated optical transceiver capabilities into cutting-edge MCMs and create advanced optical packaging and switching technologies to address the data movement demands of highly parallel systems.

The first technical area of the PIPES programme is focused on the development of high-performance optical input/output (I/O) technologies packaged with advanced integrated circuits (ICs), including field programmable gate arrays (FPGAs), graphics processing units (GPUs), and application-specific integrated circuits (ASICs). Beyond technology development, the programme seeks to facilitate a domestic ecosystem to support wider deployment of resulting technologies and broaden their impact.

The second technical area investigates novel component technologies and advanced link concepts for disruptive approaches to highly scalable, in-package optical I/O for unprecedented throughput. The objective is to answer the need for enormous improvements in bandwidth density and energy consumption to accommodate future microelectronics I/O.

The third technical area of the PIPES programme will focus on the creation of low-loss optical packaging approaches to enable high channel density and port counts, as well as reconfigurable, low-power optical switching technologies. This aims to enable the development of massively interconnected networks with hundreds to thousands of nodes that are expected due to the advance in the 2 previous areas.

The total budget is foreseen in the range of \$65M for the three areas. The selected projects have started during the second half of 2019.

#### Global view

The US effort is not limited to the above described programmes. Nevertheless, they give a vision of how the US ecosystem acts and how the priorities are defined.

Besides these activities, it is worth mentioning:

- The US AI initiative launched in February 2019;

- The National Quantum Initiative Act issued in December 2018. This initiative has announced a budget of \$1.2B to develop US leadership in quantum.

In conclusion, the US is undertaking a large research effort to maintain a dominant position in computing and to prepare the technologies that will replace the current CMOS based chips.

#### China

Assessing the efforts of China on the future of HPC technologies, is difficult as access to information related to the actual research projects is limited. This is why we have focused our analysis on the views presented in a journal<sup>10</sup> by members of the Chinese HPC ecosystem "Special Issue on Post-exascale Supercomputing" issued in November 2018.

The main challenges identified by the Chinese HPC research community are:

- 1. Energy efficiency bottlenecks: The US Department of Energy's exascale research programme sets a goal of 1 exaflops at 20–40 MW, or 25–50 gigaflops/W, probably around the year 2022. The US DARPA's JUMP programme sets a more ambitious long-term goal of 3 peta operations per second per watt, or 3 peta operations per joule (POPJ), possibly by around 2035. Here an operation is not necessarily a 64-bit IEEE floating-point operation. Cambricon-1A, which was developed at the Institute of Computing Technology of the Chinese Academy of Sciences in 2015 and targets machine learning on small terminals such as smartphones, reached over 1 tera operations per joule (TOPJ)

- 2. **Order-of-magnitude better devices**: Emerging technologies, such as 3D-stacking, fully optical communication, magnetic semiconductors, and memristors, are challenging mature technologies used in today's supercomputers which are based on CMOS

- 3. **Novel systems architectures**: Systems architecture has played a critical role in the history of modern supercomputing. Architectural innovations, from vector supercomputers, SMP, ccNUMA, and MPP, to clusters, have enabled the exponential growth of performance and scalability

- 4. Effective co-design of software and hardware: Currently, there is a wide gap between the peak performance and the sustained performance that real applications can achieve, especially with new applications with sparsity and irregularity, such as data analytics and complex multi-modal applications

- 5. **Ecosystem for diverse applications**: the existing ecosystem has a tradition of scientific and engineering computing, which is not enough for the new diverse applications that converge numeric simulation, big data, and artificial intelligence. China proposes to build up a new supercomputing ecosystem for application development, which supports the mixed or converged workloads of arithmetic-intensive, data-intensive, and intelligent applications.

In order to tackle these challenges, the Chinese researchers work on the different HPC system components.

At computing node level, the solution that is proposed in based on the following choices:

- Processor: many-core architecture with each processing core supporting scalar double precision floating-point processing instead of vector processing

- Co-processor: acceleration for specific applications, such as traditional scientific computation and engineering applications, and emerging applications including data analytics and deep learning

- Sharing of high bandwidth memory

- Inter-processor link

<sup>&</sup>lt;sup>10</sup> https://link.springer.com/journal/11714/19/10

For the network, the expected technologies will serve to interconnect large nodes that are a heterogeneous mix of central processing units (CPUs), accelerators, co-processors, and field programmable gate arrays (FPGAs)/application specific integrated circuits (ASICs). The CPUs could also be a mix of strong and weak cores. The nodes will also have a large amount of memory of different technologies, such as non-volatile random-access memory and three dimensional (3D) stacked memory. The network technologies will:

- Be heterogeneous with wired or wireless interconnects. The on-chip interconnect technology would have matured to incorporate wireless interconnection among the components within a node. Similarly, photonic technologies would have matured to be used within a node or a rack. This can provide a large number of concurrent communications among different components (CPUs, accelerators, and memories) without contention. As each node will be dense, the nodes will need to be connected to the overall network speed of terabits per second with multiple adapters/ports. This will facilitate a good balance between inter- and intra-node transfers;

- Both wireless and photonic technologies will allow the establishment of high-dimensional topologies within intra-core, intra-node, and intra-rack levels. These technologies will also facilitate one-to-many, many-to-one, and many-to-many communications in a flexible manner with a good performance

- Allow capabilities to be increasingly offloaded to the network leading to an era of 'in-network computing'

The analysis of the Chinese community is not limited to hardware technologies. In terms of software, they acknowledge that progress is also needed here if we want to have efficient post-exascale systems. The directions that are highlighted are:

- programming effort shifting from computation to data,

- precision optimization,

- programmable hardware.

In summary, the Chinese ecosystem is already working on technologies for post-exascale systems both at the hardware and software levels.

#### Japan

To analyse the situation in Japan is difficult because most of the documents are in Japanese and we do not have found a specific publication like for China which summarizes the vision of the Japanese HPC ecosystem on post-exascale technologies. However, an impression of the current Japanese efforts in technology can be given by looking at their current initiatives in the domains of supercomputing, Artificial Intelligence and quantum technologies.

#### Supercomputing

Japan has a long history of development of supercomputers. The Earth Simulator was dethroned in November 2004 as the top supercomputer in the world, but the Fujitsu's K computer, based on 68544 SPARC64 VIIIfx CPUs, each with eight cores, for a total of 548,352 core, processors developed in house, was at the top of the

TOP500 in 2011 with 10 petaflops. It was developed for RIKEN (an Institute for Physical and Chemical Research). It should be noted that the K Computer did not use graphics processors or other accelerators. The K Computer was also one of the most energy-efficient systems, and while dethroned on the TOP500, it stayed or a long time at a good position on the Green500. It was also a very "equilibrated" machine, with a good ratio compute/storage/communication, making it quite efficient on the HPCG benchmark where it was dethroned only in 2018.

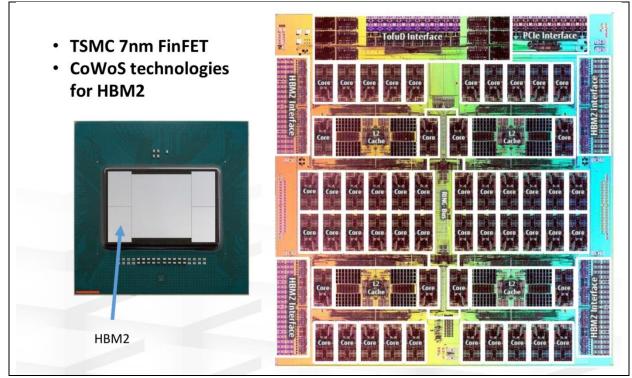

The new Japanese top system developed for the RIKEN by Fujitsu is the Fugaku<sup>11</sup> machine which is the Top500 leader since June 2020. Its computing capabilities reach more than 500 petaflops double precision floating point. in boost mode. It follows the K philosophy about being a "balanced" machine, aiming to have the best level of practicability in the world, thanks to a "codesign" approach. Unlike the US machines (Summit and Sierra) which rely on GPU to reach top performance, the Fugaku machine does not use discrete accelerator chips. Instead, the ARM v8.2-A cores, custom designed by Fujitsu, use long vector SVE (Scalable Vector Extension) extensions with a SIMD length of 512 bits developed in collaboration between ARM and Fujitsu. The chip has 48 cores (+ 2 or 4 for OS) reaching more than 2.7 teraflops per 48 cores at 2.0 GHz with boost to 2.2 GHz. The 7nm FinFET chip uses low power logic design, allowing to reach 15 GF/W @ dgemm. It should also be mentioned that the software environment is ported to the ARM processor instruction set.

FIGURE 8: THE FUJITSU A64FX CHIP, CORE OF THE FUGAKU COMPUTER.

<sup>11</sup> https://www.icl.utk.edu/files/publications/2020/icl-utk-1379-2020.pdf

The machine will have two types of nodes: Compute Node and Compute & I/O Node connected by Fujitsu TofuD, a 6D mesh/torus Interconnect.

In term of energy efficiency, the Fugaku system delivers 14.6 gigaflops/watt which is a quite impressive result for an architecture without accelerator.

#### Artificial intelligence

Japan is offering supercomputing capacities to their researchers (and companies) working on Artificial Intelligence. In 2015, The Ministry of Economy and Industry (METI) started the AIRC (Artificial Intelligence Research Center), hosted by the AIST (Advanced Institute for Science and Technologies). The 2016 budget was 19.5 billion yen. They installed the "AI Bridging Cloud Infrastructure" (ABCI) which reached about 20 petaflops in 2019. "AI Bridging Cloud Infrastructure (ABCI) is the world's first large-scale Open AI Computing Infrastructure, constructed and operated by National Institute of Advanced Industrial Science and Technology (AIST), Japan. It delivers 19.9 petaflops of HPL performance and the world's fastest training time of 1.17 minutes in ResNet-50 training on ImageNet datasets as of July 2019. ABCI consists of 1,088 compute nodes each of which is equipped with two Intel Xeon Gold Scalable Processors, four NVIDIA Tesla V100 GPUs, two InfiniBand EDR HCAs and an NVMe SSD. ABCI offers a sophisticated high performance AI development environment realized by CUDA, Linux containers, on-demand parallel filesystem, MPI, including MVAPICH, etc." (from https://insidehpc.com/2019/09/the-abci-supercomputer-worlds-first-open-ai-computing-infrastructure/).

#### Quantum computing

Japan is also active in quantum computing, but mainly in "analogue" quantum computing<sup>12</sup> (quantum annealing). There are a few start-ups on quantum computing, and also a flagship project financed by MEXT and working on transmon<sup>13</sup> based qubits (for the "universal" quantum computer). Most applications are based on combinatorial optimization for industry, transportation or traffic. Software stacks and simulations are also being developed, also for the "universal quantum" approach, e.g. by the MDR company (https://mdrft.com/)

On the hardware side, NEC is developing a superconducting flux qubit for quantum annealer, somewhat a competitor of the D-Wave machine. They claim that their forthcoming machine will be more efficient than D-Wave because they will support a more generic interconnect, event better than the new "Pegasus" interconnect of D-Wave. Optical based computing has a long history in Japan, and NTT is developing a quantum annealer based on laser and coherent ising principle. The Cabinet Office ImPACT "Quantum Neural Network" involves organizations such as NTT, NII (National Institute of Informatics). Fujitsu, Hitachi and Toshiba have

<sup>&</sup>lt;sup>12</sup> See section 3.7 for the definition of "analogue" and "universal" quantum computers

<sup>&</sup>lt;sup>13</sup> A **transmon** is a type of <u>superconducting charge qubit</u> that was designed to have reduced sensitivity to charge noise. The transmon was developed by <u>Robert J. Schoelkopf</u>, <u>Michel Devoret</u>, <u>Steven M. Girvin</u> and their colleagues at <u>Yale</u> <u>University</u> in 2007 (from Wikipedia)

digital solutions for the hardware implementation of simulated annealing. Fujitsu's Digital Annealer<sup>14</sup> is an ASIC which can be used as coprocessor. The first generation (1024 "bits" with 16 bits inter-bit coupling accuracy) is accessible by the cloud, while the second generation will support 8192 "bits" with 64 bits for coupling accuracy. By combining chips by software, the 2019 servers can support up to 1M "bits". Hitachi has developed a CMOS Annealing machine<sup>15</sup>. Toshiba<sup>16</sup> is developing hardware to support their quantum-inspired algorithm "Simulated Bifurcation Algorithm".

<sup>&</sup>lt;sup>14</sup> https://www.fujitsu.com/global/services/business-services/digital-annealer/index.html

<sup>&</sup>lt;sup>15</sup> https://www.hitachi.com/rd/portal/contents/story/cmos\_annealing2/index.html

<sup>&</sup>lt;sup>16</sup> https://www.toshiba-sol.co.jp/en/pro/sbm/sbm.htm

### Potential options for the future HPC technologies

This section presents the main technical findings about how the electronics and photonics technologies will impact the future HPC system. This information is a synthesis of the discussions undertaken with the electronics and photonics ecosystems and of the analysis of other technical documents.

#### Introduction

Today's HPC system architecture is dominated by the standard CPU+GPU<sup>17</sup> solution. This architecture has been effective at offering the performance increase requested by HPC users while challenging them to exploit the massive parallelism and heterogeneity offered by this solution.

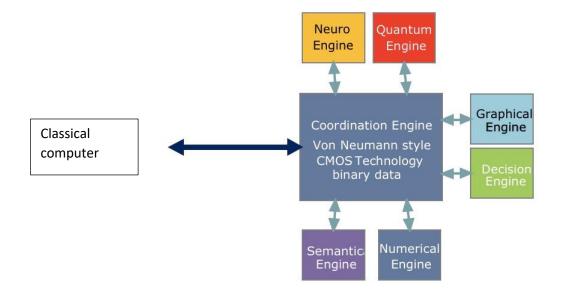

We foresee little changes in the 2020-2023 time frame with the first exascale systems based on this approach. After sustaining the growth in the number of operations per watt, new solutions will have to be found as Moore's law will fade and Dennard's scaling gone. Progress can be made in three axes:

- New architectures

- New data representation schemes

- New technologies (compared to CMOS<sup>18</sup>)

Most of the new approaches are a combination of the three (or at least of two of them) but it is important to understand that we have these three freedom degrees that can be played with:

- Switching from computing centric execution used by processors and GPU (akin to Von Neumann architecture) to the data centric paradigm to reduce the overhead introduced by the data movement;

- Changing what is called an operation by playing with operand precision or introducing multi-bits or analogue coding or other ways of encoding information (e.g. Quantum),

- Introducing new materials that will deliver more efficient way (in terms of timing and/or energy) to store, switch and/or process information.

This gives a very broad set of options but only a few will emerge due to economic constraints, critical mass issues, industrialization aspects, legacy and usability problems. The following sections present some of the most promising paths.

<sup>&</sup>lt;sup>17</sup> Computing Processor Unit + Graphical Processor Unit

<sup>&</sup>lt;sup>18</sup> Complementary Metal Oxide Semi-conductor

#### Enhancements of current CMOS technologies

#### CMOS scaling

Even if we are close to the limit of CMOS scaling, there is still room for improvement in this domain. The leading foundries (TSMC, Intel, Samsung) are investigating for at least 2 more technology nodes compared to their current technologies. This could provide a way of putting roughly about 4 times more transistors in the same surface of silicon compared to today. However, this scaling comes with the cost of very expensive equipment (e.g. Extreme ultraviolet lithography - *EUV* or *EUVL*), and the power density of those technologies is still not known, perhaps limiting the number of devices active at the same moment on the die. It should also be noted that even if the technology nodes are labelled with the same name (e.g. 7nm), all these nodes might not be equivalent:

| Nominal |                  |             |             |           |       |           |               |           |                     |                                                                                                                                                                        | 5nm         |

|---------|------------------|-------------|-------------|-----------|-------|-----------|---------------|-----------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| node    |                  | 28nm        | 22nm        | 20nm      | 18nm  | 16nm      | 14nm          | 12nm      | 10nm                | 7nm                                                                                                                                                                    | (ITRS)      |

|         | Lg               |             | 24          |           |       |           | 20            |           | 16                  | ~12nm                                                                                                                                                                  | 10          |

|         | Fin Pitch        |             | 60 FinFET   |           |       |           | FinFET 42     |           | FinFET 34           | FinFET                                                                                                                                                                 | 12          |

|         | CPP              |             | 90          |           |       |           | 70            |           | 54                  |                                                                                                                                                                        | 32          |

| Intel   | M1               |             | 80          |           |       |           | 52            |           | 36                  |                                                                                                                                                                        | 16          |

| inter   | SRAM             |             | HD 0.092µm2 |           |       |           | 0.0588µm2     |           | 0.0312µm2           | 0.027µm2                                                                                                                                                               |             |

|         | Year Publication |             | VLSI 2012   |           |       |           | IEDM 2014     |           | IEDM 2017/ISSCC2018 | IEDM 2016                                                                                                                                                              |             |

|         | Risk Prod        |             | 2011        |           |       |           | 2014          |           | 1Q18                |                                                                                                                                                                        |             |

|         | Lg               | 32          |             | 25        | 25    |           | 30            |           | ~20                 | ~16                                                                                                                                                                    |             |

|         | Fin Pitch        | BULK        |             | BULK      | FDSOI |           | 48 FinFET     |           | Single Fin 42       | Dual thin EUV 27                                                                                                                                                       |             |

| Samsung | CPP              | 114         |             | 86        | 86    |           | 78            |           | 68                  | 54/57                                                                                                                                                                  |             |

|         | M1               | 90          |             | 64        | 64    |           | 64            |           | 51                  | 36                                                                                                                                                                     |             |

|         | SRAM             | 0.152µm2    |             | 0.084µm2  |       |           | 0.064/0.08µm2 |           | 0.04µm2             | HD 6T SRAM 0.026µm2                                                                                                                                                    |             |

|         | Year Publication | ICSIST 2011 |             | VLSI 2012 |       |           | JSSC 2014     |           | ISSCC/VLSI 2017     | VLSI 2017/ISSCC2017-2018                                                                                                                                               | 16<br>7<br> |

|         | Risk Prod        | 2011        |             | 2013      |       |           | 4Q-2015       |           | 1Q2017              | 2H-18                                                                                                                                                                  |             |

|         | Lg               | 30          | 30          | 30        |       | 33        |               | 25        | ~20                 | ~16                                                                                                                                                                    |             |

|         | Fin Pitch        | BULK        | BULK        | BULK      |       | FinFET 45 |               | FinFET 45 | FinFET              | FinFET 4th                                                                                                                                                             |             |

|         | CPP              | 118         | 105         | 90        |       | 90/80     |               | 90/80     | 64                  | 57                                                                                                                                                                     |             |

| TSMC    | M1               | 90          | 80          | 64        |       | 64        |               | 64        | 42                  | 40                                                                                                                                                                     |             |

|         | SRAM             | 0.155µm2    | 0.155µm2    |           |       | 0.07µm2   |               |           | 0.03µm2             | "12nm 10   FinFET 12   32 32   16 32   0.027µm2 8   8 IEDM 2016   °16 54/57   36 54/57   HD GT SRAM 0.026µm2   VLSI 2017/ISSC2017-2018   2H-18   ~16   FinFET 4th   57 |             |

|         | Year Publication |             | VLSI 2012   | VLSI 2014 |       | IEDM 2013 |               | 6Track    | VLSI 2016           |                                                                                                                                                                        |             |

|         | Risk Prod        | 2011        | 2018        | 2013      |       | 4Q-2015   |               | 3Q2016    | 4Q2016              | 3Q-17                                                                                                                                                                  |             |

|         | Lg               |             | 28          |           |       |           | 30            |           |                     |                                                                                                                                                                        |             |

|         | Fin Pitch        |             | FDSOI       |           |       |           | 48 Fin FET    |           |                     |                                                                                                                                                                        |             |

|         | CPP              |             | 90          |           |       |           | 78            |           |                     |                                                                                                                                                                        |             |

| GF      | M1               |             | 78          |           |       |           | 67            |           |                     |                                                                                                                                                                        |             |

|         | SRAM             |             | 0.110µm2    |           |       |           | 0.110µm2      |           |                     |                                                                                                                                                                        |             |

|         | Year Publication |             | IEDM 2016   |           |       |           | IEDM 2016     |           |                     | C.Reita, C.Fenouillet-                                                                                                                                                 |             |

|         | Risk Prod        |             | 2016        |           |       |           | 2H-2016       |           |                     | Beranger - CEA-LETI - 2018                                                                                                                                             |             |

FIGURE 9: NOMINAL VS. ACTUAL NODE DIMENSIONS (SOURCE: CEA LETI)

CMOS scaling is also related to the evolution of the structure of the transistor. After FDSOI<sup>19</sup> and FinFet<sup>20</sup>, the structure of the transistor could be based on silicon nanosheets.

In this domain, one of the challenges for Europe is that these technologies will only be developed by foreign players. As HPC system performance is highly dependent on density, the most advanced chips are mandatory and Europe need to have access to these technologies. This a strategic risk that needs to be monitored.

<sup>&</sup>lt;sup>19</sup> Fully Depleted Silicon On Insulator

<sup>&</sup>lt;sup>20</sup> fin field-effect transistor

On the technology side, the challenge for the last CMOS technology nodes is to get a reduction of the energy by transistor while increasing the number of transistors. Even if we cannot expect as in the past a decrease of the energy by the same factor as the increase of transistors, progress in energy efficiency is mandatory to make the new CMOS technology nodes a success for HPC systems.

#### 2.5/3D stacking

2.5D/3D stacking provide a way of reducing the latency and energy and avoiding package bandwidth bottlenecks when we want several chips to communicate together. 2.5 D stacking is the concept of small dies (called chiplets) integrated on a common substrate (the interposer) that can be organic, passive silicon, active silicon or using photonic technologies. 3D stacking is the stacking of layers of integrated circuits on top of each other. It can be done either by wafer to wafer, chip to wafer stacking, or by monolithic 3D which allow a finer granularity (down to the level of transistors). HPC is already benefiting from this technology with the first HPC systems using high bandwidth memory (HBM or HMC<sup>21</sup>) and processor manufacturers (AMD, Fujitsu, Intel...) having already used 2.5D in the latest products. The boost in memory bandwidth is a great improvement for memory bound applications and a must for architectures with accelerators that require this kind of bandwidth to deliver their performance. 2.5D also allows for mixed chiplets with various technologies, and for example, with active interposers, having power conversions integrated "in the chip", providing globally a better energy efficiency.

It can also be a path for production of hybrid packages mixing chips of different architectures (see Section 3.3) or even chips manufactured with different technologies (see Section 3.5) Nevertheless, stacking "compute" chips with a higher heat dissipation than memory chips leads to thermal problems that today limit the number of chips that could be put in a package.

Europe is present in this field with excellent know-how in the three main RTOs<sup>22</sup> and some research installations to test new concepts. For an industrial development, as "High end" computing is more and more important for the automotive market (Advanced Driver Assistance Systems and self-driving), the European automotive industry might be a driver for having European actors in 2.5 D and the integration of complex systems on dies or interposers.

The European EPI (European Processor Initiative) plans to use2.5 D technology, in the same way as AMD, Intel and Fujitsu.

In this domain, one of the main technical challenges is the thermal dissipation of the stack. Innovations are needed to solve this problem before 3D stacking can scale and deliver all of its promises.

Another challenge is the set-up of European industrial options. Even if today the RTOs have research installations to design new concept chips, the industrial solutions are mainly coming from Asia. Having a

<sup>&</sup>lt;sup>21</sup> High Bandwidth Memory and Hybrid Memory Cube

<sup>&</sup>lt;sup>22</sup> Research and Technology Organizations: CEA, Fraunhofer, IMEC

European based option would be important from an independent and economic stand point because of the potential of this technology.

To foster the development of European chiplets that can be integrated via 2.5/3D stacking, it could also be strategic to work on integration standards. Having a commonly defined interface will provide an exploitation path for new initiatives in the area of accelerator design.

#### Precision of operations

The trend in the past has been to provide more and more precision for operations as HPC was focused on simulations where stability and convergence of algorithms depended on this feature. Today, for new applications coming mainly from neural networks, high precision is not mandatory (the "learning phase of Deep Neural Networks can be done in most case with 16-bits floating point operations) and switching to low precision can save space (i.e. transistors and data paths) and energy.

The availability of 16 and 8 bit operations in processors and accelerators is a trend that will allow to adapt precision to the needs of algorithms with an important saving in some cases.

On the reverse side, sometimes convergence of algorithms could benefit from high precision to reduce the number of iterations and to save time and energy. New coding schemes are possible and alternative to the IEEE 754 arithmetic, like UNUM<sup>23</sup>. Its implementation in processors could be more efficient then software emulation of this high precision scheme.

The trend, to have flexibility in the representation of data, is a challenge for software development. The choice of the representation could be made automatically with analysis of the pro and cons of the different options. This could lead to the automatic selection of libraries optimized for different data formats.

This rethinking of data representations is also a precursor to a more disruptive approach with the use of analogue options (see Section 3.6).

#### New architectures

Today standard processors and GPU accelerators are based on a Von Neumann architecture where a controlled execution applies operations onto data that are stored in registers (fed by caches, fed by memory). This architecture is very flexible but can be costly in terms of transistor, data paths and energy compared to what is just needed for an application. This implies a lot of moves and duplications of data, which is not efficient (bringing data from external memory is 3 orders of magnitude more energy demanding than a floating-point operation on those data). However, there is a research path what proposes architectures that will be more efficient for some classes of problems. Some of these new architectures can be implemented using standard

<sup>&</sup>lt;sup>23</sup> Universal Number

CMOS technology or providing opportunities to introduce new technologies that will be more efficient than CMOS (see section 3.5).

Some concepts of new architectures are generic (see section on data flow or IMC<sup>24</sup> below) or target a specific class of algorithms (see section on neuromorphic, graph and simulated annealing below).

#### Data flow

In data flow architectures, data move between modules that perform the computation on the data. You do not have any program counter that controls the execution of the instructions as in a Von Neumann architecture. Deep Learning architecture (see section on neuromorphic architecture below) can be implemented as a specific dataflow architecture (the main operations are matrix-based). The investigation of dataflow architectures is linked to FPGA (Field Programmable Gate Array) as most of the ideas have not led to the tape out of specific circuits but have been tested and implemented with FPGA.

With the slowdown of standard processors performance increase, development of data flow architectures can provide an alternative to deliver this performance increase. The development of reconfigurable architectures (like the Intel CSA Configurable Spatial Accelerator) and progress toward flexible reconfigurable FPGA will be an asset for implementing data flow architectures.

#### IMC/PIM (In memory computing/Processor in memory)

These architectures couple the storage with some computing capabilities. The idea is that bringing the computation to the memory will be cheaper in resources than moving data to the computing units. Most of the time this approach is mixed with a standard architecture to allow computation on several data.

The architecture is also related to the development of Non-Volatile Memory (see Section 3.4) and appealing as long as the cost of the in-memory computation is low.

#### Neuromorphic

The development of AI, and especially applications using Deep Learning techniques, has led to a huge interest for neuromorphic architectures that are inspired by a theoretical model of a neuron. This architecture can be used for AI tasks but can also be viewed as a generic classification function or a function approximation.

As more and more applications (or a part of an application) are mapped to this paradigm, it is worth developing specific circuits that implement only the operations and data paths mandatory for this architecture. Several examples already exist such as the Google Tensor Processing Unit chip or Fujitsu Deep Learning Unit chip.

<sup>&</sup>lt;sup>24</sup> In Memory Computing

These efforts have not exploited all the possible options and have not developed all the interesting features of the architecture, so research in this area is still valuable.

We can distinguish various kind of possibilities:

- 1. Using classical digital arithmetic, but designing more specialized architectures (examples: TPU and DLU)

- 2. Using another way of coding information, like "spikes" or their representation in AER coding (Address-Event Representation) (see fig 12).

- 3. Using « physics » to make computation (e.g. Ohms law for products and Kirchhoff law for summation; see Section 3.6 "Analog computing").

Of course, the approaches can be combined. Typically, most people call "neuromorphic" the approaches using option 2, because it is closer to the way the nervous system communicates.

One important aspect is that this architecture is a good candidate to introduce an alternative to CMOS (see Section 3.5).

| NG NEURO-INSPIRED: "SPIKING" NEURAL NETWORKS<br>Jsing another way of coding informationnot using bits |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |                      |      |  |  |  |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|------|--|--|--|

|                                                                                                       | IBM<br>TrueNorth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Intel Loihi         | DynapSEL             | **** |  |  |  |

| Technology                                                                                            | 28nm CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14 nm CMOS          | 28 nm FDSOI          |      |  |  |  |

| Supply Voltage                                                                                        | 0.7-1.05 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.5-1.25 V          | 0.73-1 V             |      |  |  |  |

| Design Type                                                                                           | Digital                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Digital             | Mixed-signal         |      |  |  |  |

| Neurons per core                                                                                      | 256                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Max 1k              | 256                  |      |  |  |  |

| Core Area                                                                                             | 0.094 mm <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.4 mm <sup>2</sup> | 0.36 mm <sup>2</sup> |      |  |  |  |

| Computation                                                                                           | Time multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Time multiplexing   | Parallel processing  |      |  |  |  |